# MICRO-428: Metrology

Edoardo Charbon, Claudio Bruschini, Georg Fantner

Institute of Electrical and Micro Engineering (IEM), School of Engineering (STI)

Ecole polytechnique fédérale de Lausanne (EPFL), Neuchâtel, Switzerland

TAs: Samuele Bisi, Alexandre Domenech

**EPFL**

# MICRO-428: Metrology

Week Twelve: Electrical Metrology

Claudio Bruschini

TA: Alexandre Domenech

Paul Mos

Advanced Quantum Architectures Laboratory (AQUA)

EPFL at Microcity, Neuchâtel, Switzerland

**EPFL**

# Reference Books

---

B. Razavi, *Design of Analog CMOS Integrated Circuits*, McGraw Hill., 2017

# Week 11 Summary

---

## 11.1 Noise reduction: filtering; averaging techniques – effect on signal and noise:

$Var\{N_{avg}\} = \frac{1}{n}\sigma^2$  and  $SNR_{avg, identical\ sign.} = n\ SNR$  (replicate measurements, signal  $s(t)$

uncorrelated to noise, and noise  $z(t)$  uncorrelated; also valid when there are different (additive) independent noise sources)

## 11.2 Electric Signals, Analog-to-Digital Conversion: Sampling and Holding (S/H), Quantizing and Encoding (Q/E)

**Parameters:** resolution, Differential non-linearity (DNL), Integral non-linearity (INL), Quantization noise ( $\sigma_{noise}^2 = \Delta^2/12$ ), Signal-to-quantization-noise ratio ( $SQNR = 20\log_{10}(2^Q) \approx 6.02 \cdot Q + 1.76$ )

**ADC architectures:** Integrating, Successive-Approximation, (Charge-redistribution,) Flash (Direct Conversion), Pipelined

11.3 **Timing – Time-to-Digital Conversion:** Non-idealities, DNL, INL, optical tests (single-shot precision, code density test)

**TDC architectures:** Counter – Register, Delay Chain, Vernier Lines, Ring Oscillator

**Application Examples:** Time-resolved imaging (ToF, FLIM, PET, Raman, ...)

**Technique:** Time-correlated single-photon counting (TCSPC)

# Outline

---

10.1 Charges, Currents, and Voltages

10.2 Noise Background

10.3 Noise Sources

11.1 Noise Reduction, Averaging Techniques

11.2 Electric Signals, Analog-to-Digital Conversion

11.3 Timing – Time-to-Digital Conversion

**12.1 Electrical Metrology Tools**

# Outline

---

12.1.1 Phase-Locked Loops (PLL)

12.1.2 Lock-in Amplifier

12.1.3 Other Tools for Electrical Metrology

Appendix A: PLL Analogies

## 12.1.1 PLL: Phase-locked Loop

- Phase-locked Loop (PLL) is an **Electronic Module (control circuit)** that **locks** the **phase** of the **output** to the **input** (which also implies keeping the input and output frequencies the same) -> coincident rise (fall) edges

- «The PLL helps keep parts of our world orderly.» (*Henri de Bellescize, 1932*)

- «If we turn on an analogue television set, a PLL will keep heads at the top on the screen and feet at the bottom. In color television another PLL makes sure that green remains green and red remains red even if the politicians claim that the reverse is true. » (attributed to *Henri de Bellescize*)

- Why do I need it if I already have an input signal?

Examples of uses: **Frequency Multiplications** (with the base accuracy of the reference), **Clock Skew and/or Jitter Reduction** (to counteract inter/intra-chip propagation errors)

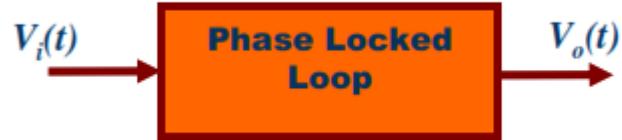

## 12.1.1 PLL Basics

---

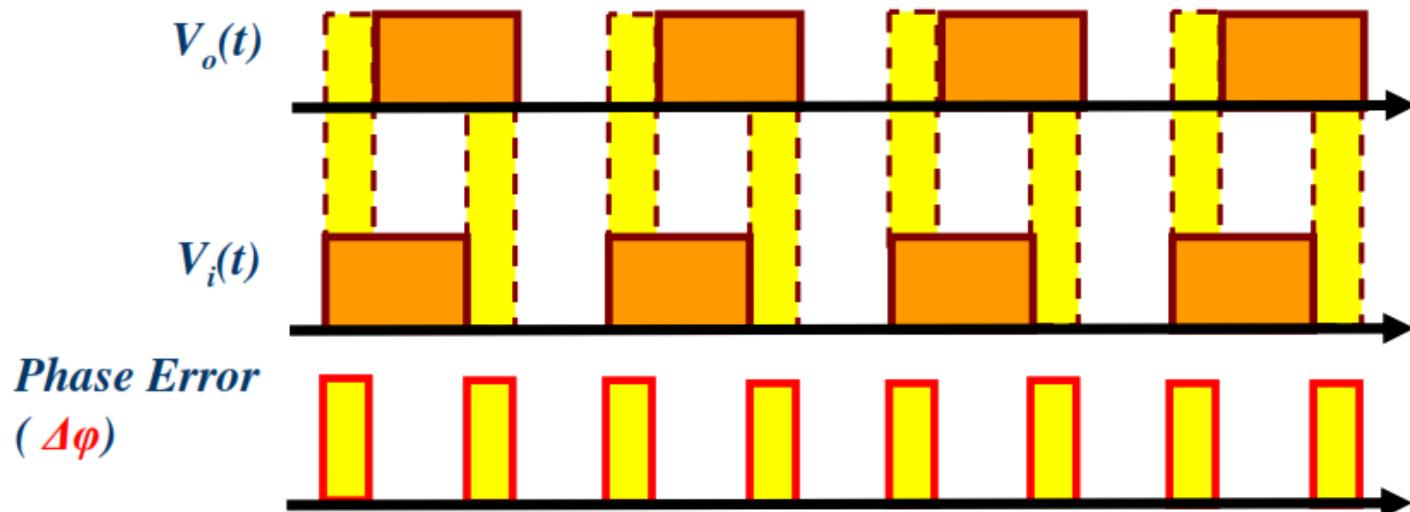

- Example of locked phase:

## 12.1.1 PLL Basics

- Example of unlocked phase:

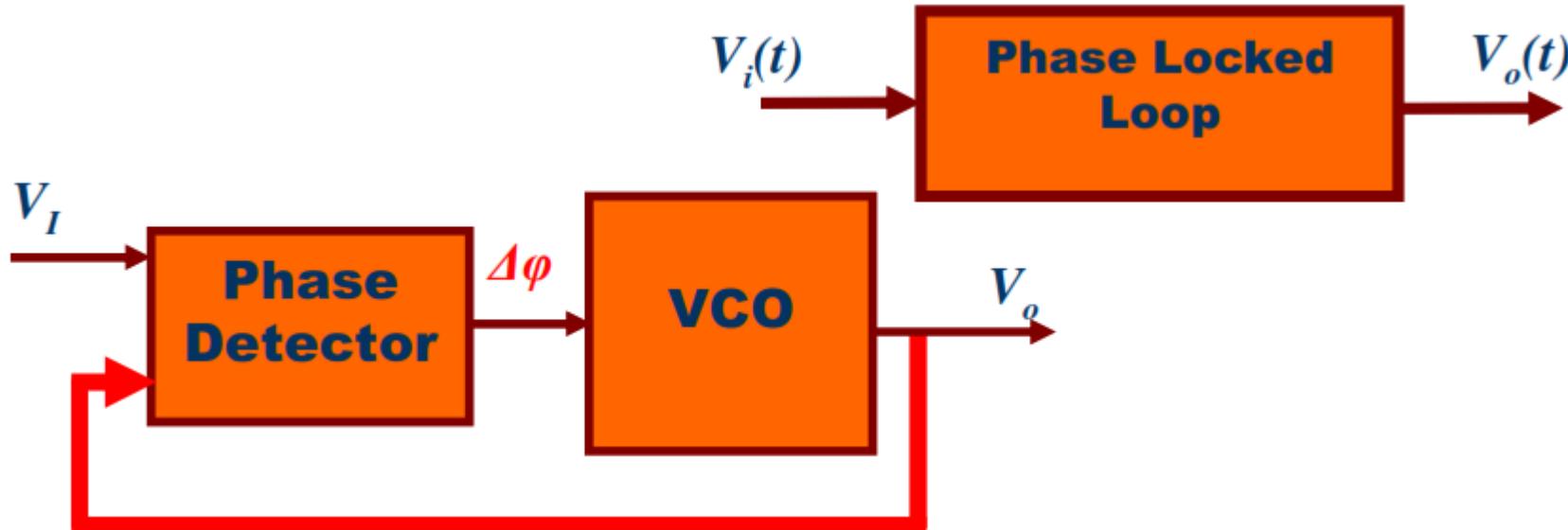

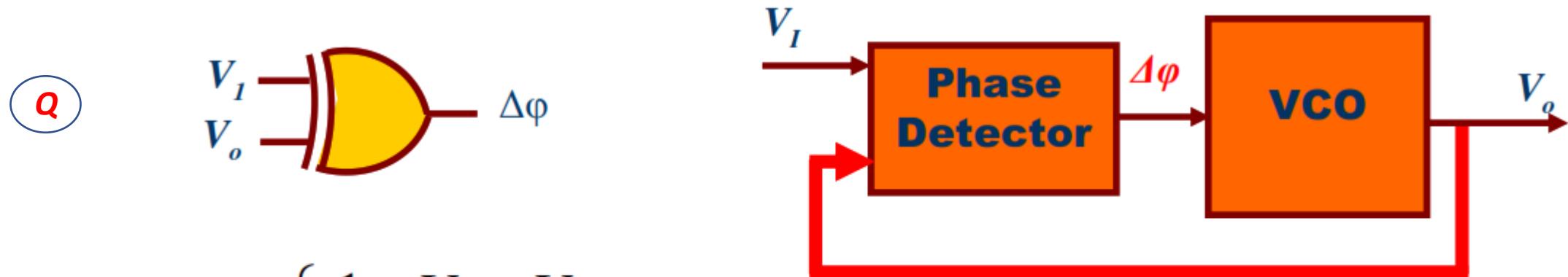

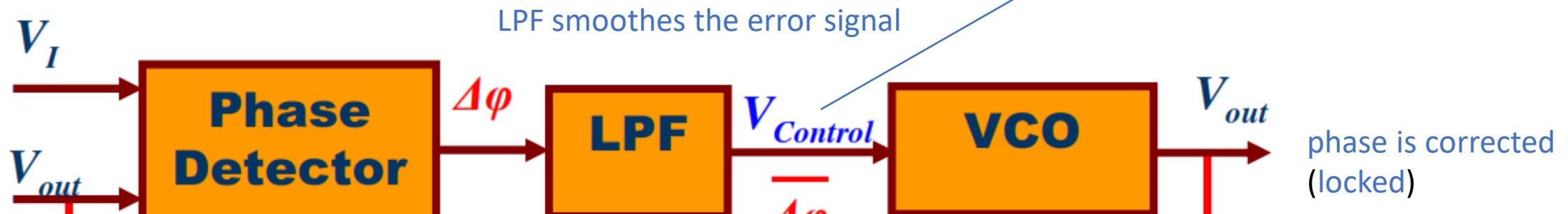

## 12.1.1 PLL Basics – Phase detector + VCO

- PLL is a **feedback** system that **detects** the phase error  $\Delta\varphi$  and then **adjusts** the phase of the output.

- Phase Detector (PD) detects  $\Delta\varphi$  between the output and the input through a feedback system.

- Voltage-Controlled Oscillator (VCO) adjusts the phase difference.

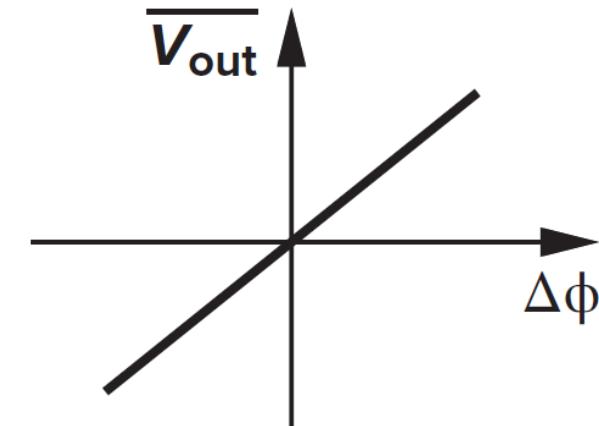

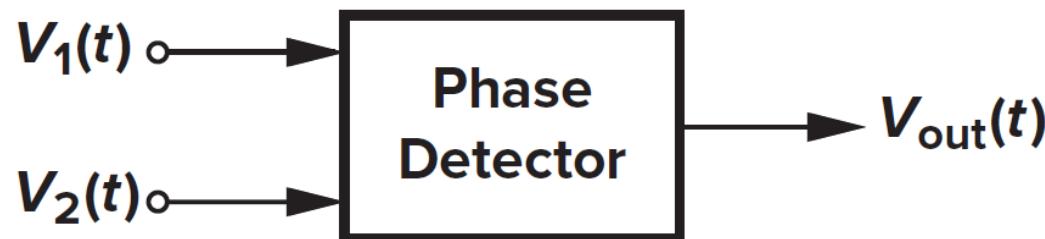

## 12.1.1 PLL – Phase Detector

- A **phase detector** is a circuit whose average output is linearly proportional to the phase difference,  $\Delta\varphi$ , between its two inputs ( $V_1(t)$  and  $V_2(t)$ ).

- In the ideal case, the relationship between  $V_{\text{out}}$  and  $\Delta\varphi$  is linear, crossing the origin for  $\Delta\varphi = 0$ .

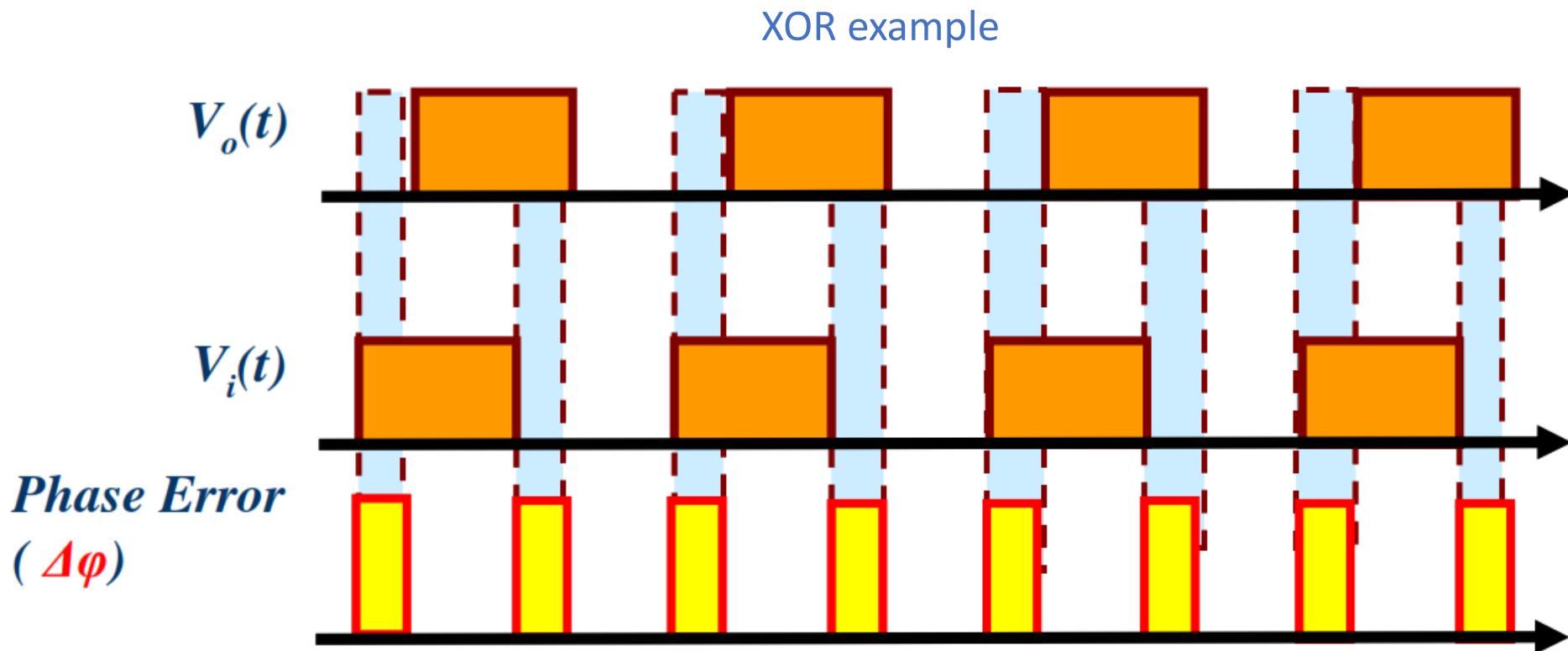

## 12.1.1 PLL – Phase Detector (XOR Gate)

- A familiar example of phase detector is the exclusive OR (XOR) gate.

$$\Delta\varphi = \begin{cases} 1 & V_I \neq V_o \\ 0 & V_I = V_o \end{cases}$$

- As the phase difference between the input varies, so does the width of the output pulses, thereby providing a DC level proportional to  $\Delta\varphi$ .

| $V_o$ | $V_I$ | $\Delta\varphi$ |

|-------|-------|-----------------|

| 0     | 0     | 0               |

| 0     | 1     | 1               |

| 1     | 0     | 1               |

| 1     | 1     | 0               |

## 12.1.1 PLL – Phase Detector (XOR Gate)

- While the XOR circuit produces **error pulses** on both **rising** and **falling** edges, other types of **Phase Detectors** may respond **only** to **positive** or **negative** transitions.

- The operation of **phase detectors** is similar to that of **differential amplifiers** in that both **sense** the **difference** between the **two inputs**, **generating** a **proportional** output.

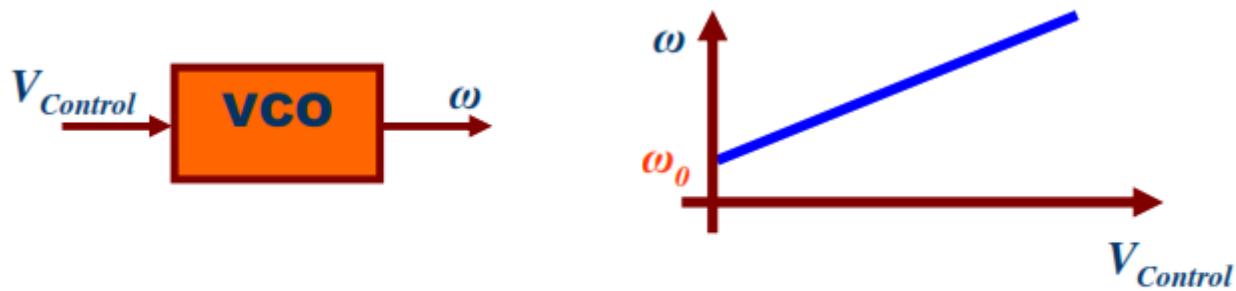

## 12.1.1 PLL – Voltage-Controlled Oscillator (VCO)

- VCO is a circuit model that oscillates at a controlled frequency  $\omega$ .

- The Oscillating Frequency is controlled using voltage  $V_{\text{control}}$ .

$$\omega = \omega_0 + K_{VCO} V_{\text{Control}}$$

- Note: if we have a single control input ( $V_{\text{control}}$ ), we must vary the frequency to vary the phase!

B. Razavi, "Design of Analog CMOS Integrated Circuits", McGrawHill 2017

## 12.1.1 Simple PLL

- $V_{control}$  must be in the **steady state** («remain quiet») for the VCO to operate properly. However, the Phase Detector output, i.e. the phase error  $\Delta\varphi$ , consists of a dc component (desirable) and high-frequency components (undesirable) -> filtering of Phase Detector output needed.

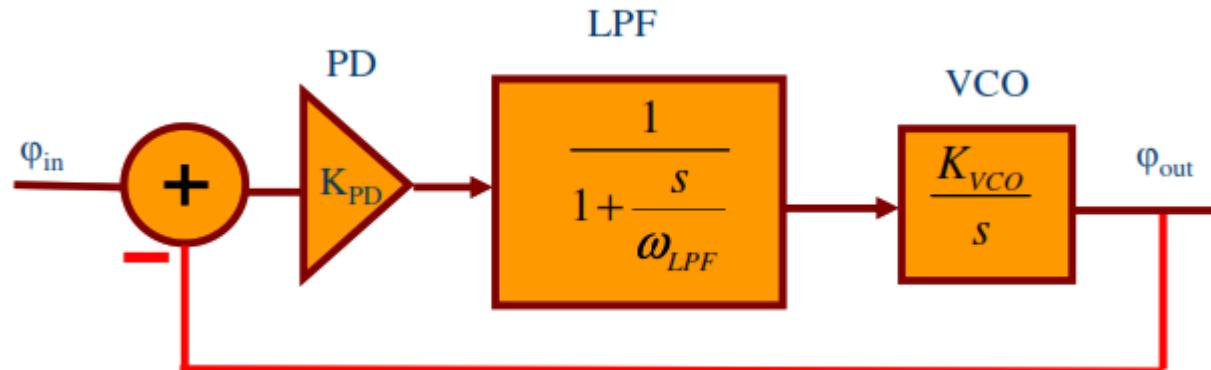

-> **Simple PLL consists of three basic functional blocks:**

- ❖ Phase Detector (XOR) that detects the phase error  $\Delta\varphi$

- ❖ Low Pass Filter (LPF) to smooth  $\Delta\varphi$

- ❖ Voltage-Controlled Oscillator

slows down or speeds up the VCO module

## 12.1.1 PLL - Locked Condition

- Locked Condition:

$$\phi_{out}(t) - \phi_{in}(t) = \text{constant} \rightarrow \frac{d}{dt}(\phi_{out} - \phi_{in}) = 0$$

- This implies that

$$\omega_{in} = \omega_{out}$$

- An important and unique consequence of **phase locking** is that the **input** and **output frequencies** of the PLL are **exactly equal**.

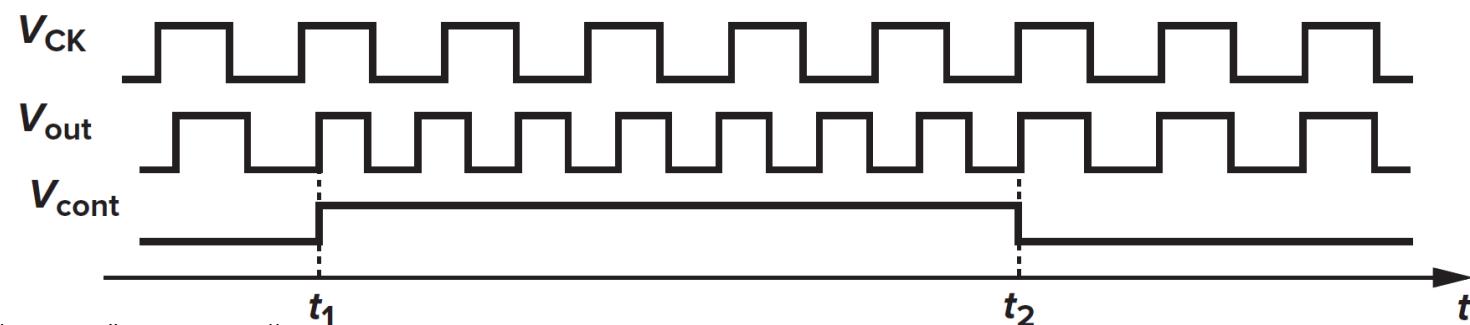

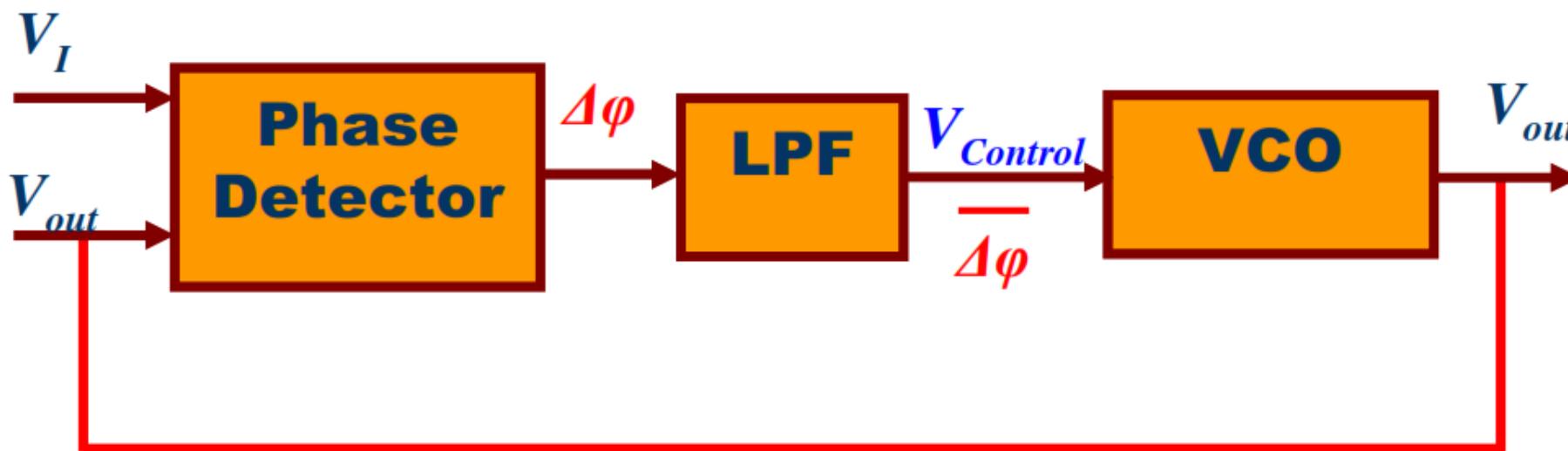

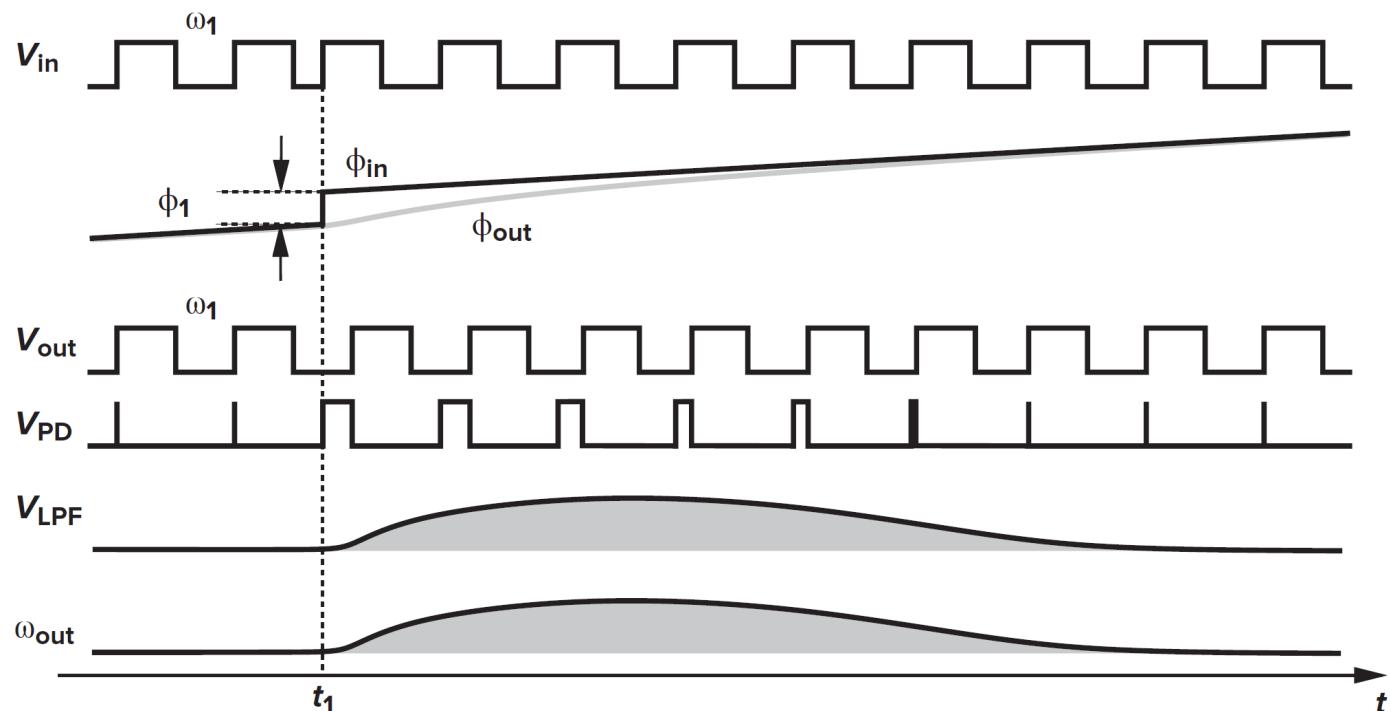

## 12.1.1 PLL - Locked Condition, Small Transients

- For simplicity, let's assume:

Locked conditions  $V_{in} = V_A \cos(\omega_1 t)$ ,

$V_{out} = V_B \cos(\omega_1 t + \varphi_0)$

+ phase error (e.g. a **phase step**):

$$\Delta\varphi = \phi_1 u(t - t_1) \rightarrow \phi_{in} = \omega_1 t + \phi_1 u(t - t_1)$$

-> The **Phase Detector** creates  $V_{control}$  and VCO will change:

$$\omega_{out} = \omega_1 + K_{VCO} V_{control}$$

- When the loop settles, the output voltage becomes:

$$V_{out} = V_B \cos(\omega_1 t + \varphi_0 + \Delta\varphi(t))$$

**Response of a PLL to a phase step**

$V_{control}$  rises gradually, VCO frequency begins to change

Loop is not locked during the transient ( $\Delta\varphi$  varies with time)

$\omega_{out}$  must eventually go back to  $\omega_1$

$\phi_{out}$  gradually catches up with  $\phi_{in}$

All the parameters assume their original values

## 12.1.1 Dynamics of Simple PLL (transient behaviour)

B. Razavi, "Design of Analog CMOS Integrated Circuits", McGrawHill 2017

## 12.1.1 Dynamics of Simple PLL (transient behaviour)

- Exact transient (settling) behaviour in general: PLL is a feedback system

-> **Linear model:**

PD is a gain amplifier

LPF is a first order filter (as an example)

VCO is a unit step module

B. Razavi, "Design of Analog CMOS Integrated Circuits", McGrawHill 2017

## 12.1.1 Dynamics of Simple PLL (transient behaviour)

- The (closed loop) transfer function of the system (which determines how the output phase tracks the input phase) will be:

$$H(s) = \frac{\Phi_{out}}{\Phi_{in}}(s) = \frac{\omega_{out}}{\omega_{in}}(s) = \frac{K_{PD}K_{VCO}\omega_{LPF}}{s^2 + \omega_{LPF}s + K_{PD}K_{VCO}\omega_{LPF}}$$

which we can rewrite as ( $\omega_n$  = natural frequency,  $\zeta$  = damping factor):

$$H(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(2<sup>nd</sup> order transfer function, two poles)

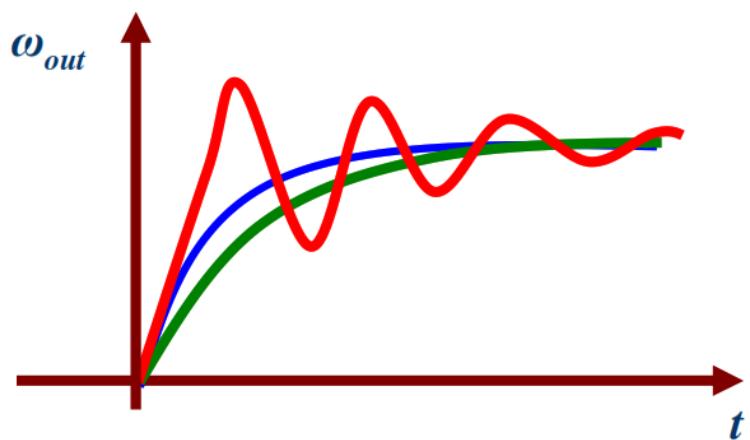

## 12.1.1 Transient response of a PLL

- Unit (frequency) step response of a second order system:

Overdamped

Critically damped

Underdamped

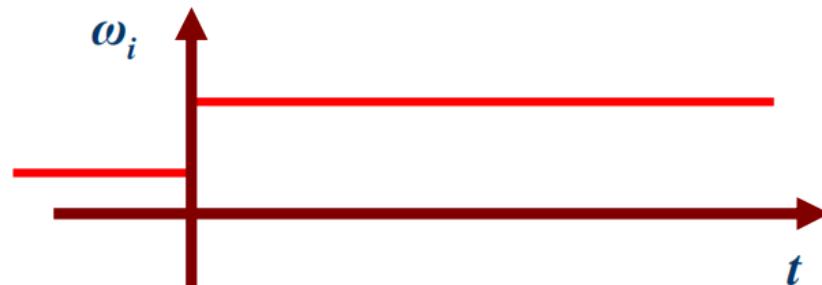

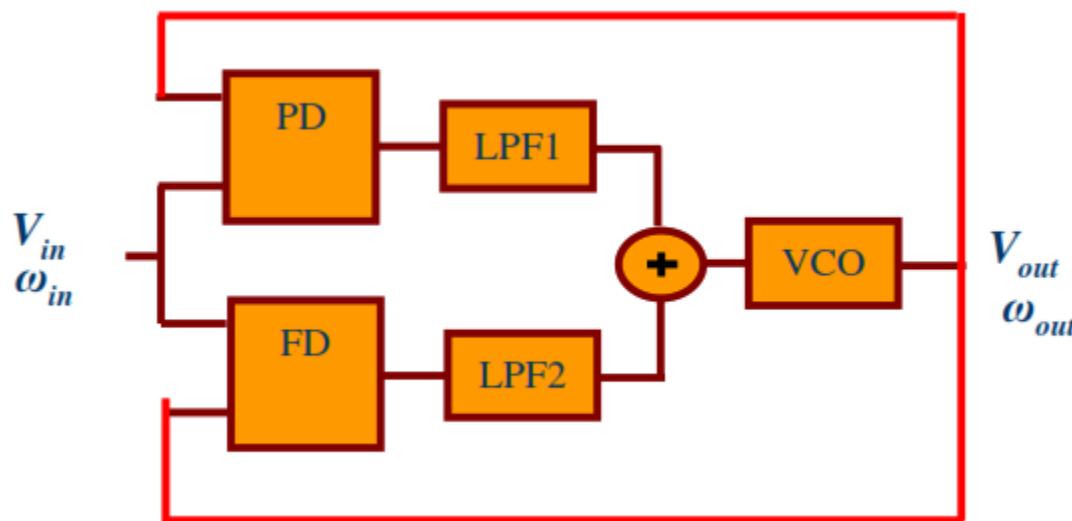

## 12.1.1 PLL Lock Acquisition Problem

- Suppose that, when the PLL is turned on, the output frequency is far from the input frequency

- It is possible that the PLL would never lock

- Modern PLL uses Frequency Detector (FD) in addition to the Phase Detector (PD)

At the beginning, the FD drives  $\omega_{out}$  toward  $\omega_{in}$  while the PD output remains “quiet.” When  $|\omega_{out} - \omega_{in}|$  is sufficiently small, the phase-locked loop takes over, acquiring lock.

## 12.1.1 PLL Applications

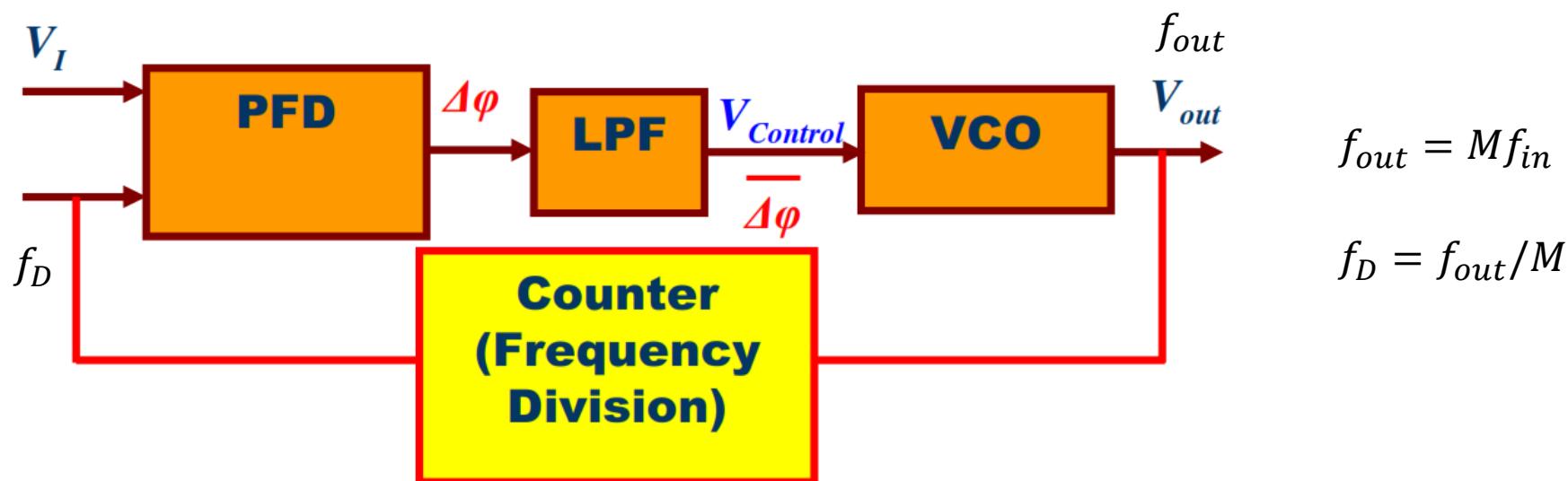

### 1. Frequency Multiplications (PLL multiplies input frequency by M):

- The feedback loop has frequency division

- Frequency division is implemented using a counter (one output pulse every M input pulses)

<https://www.youtube.com/watch?v=kOAUw0W138> (16:00)

## 12.1.1 PLL Applications

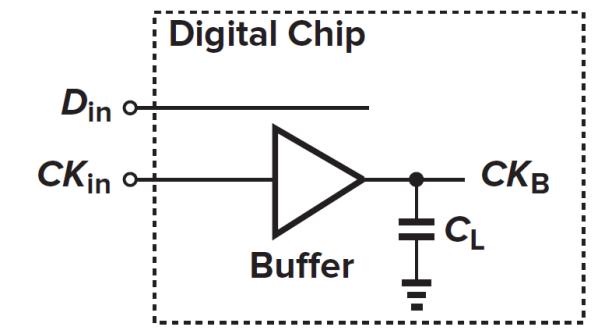

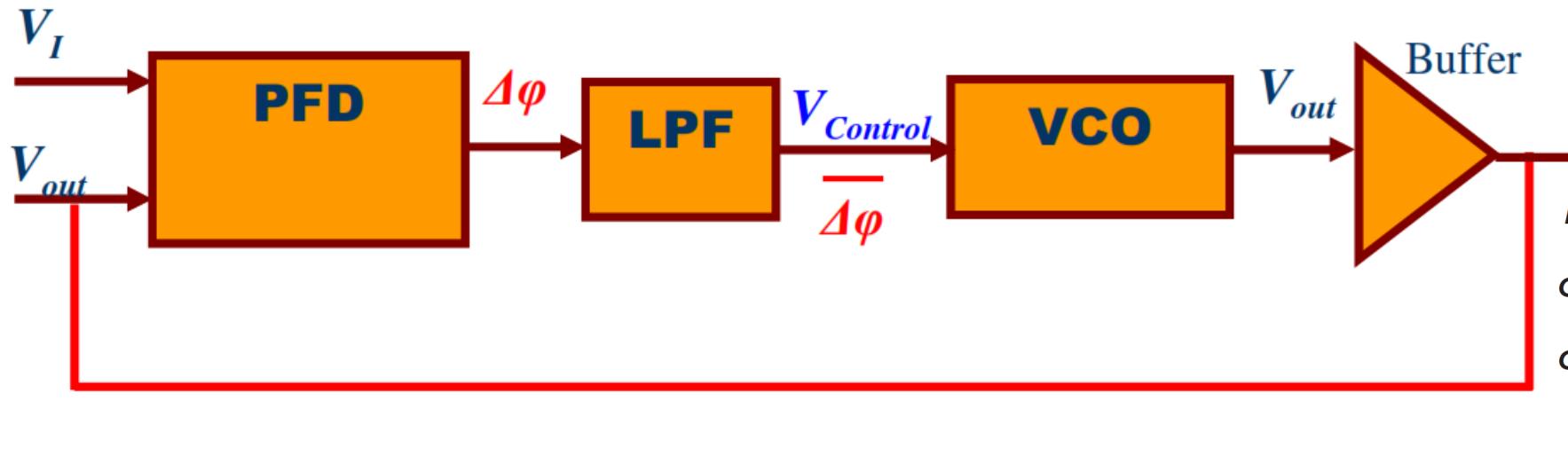

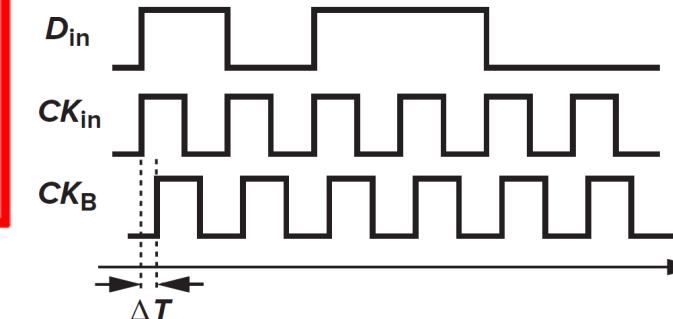

### 2. Clock Skew Reduction

Buffers (buffer amplifiers) are routinely used to distribute the clock (to drive a large number of transistors and long interconnects) -> may result in large skews (phase shifts)

-> Can be corrected with a PLL by embedding the buffer within the PLL loop

$D$  = data,  $CK$  = clock

## 12.1.1 PLL Applications

### 3. Jitter Reduction

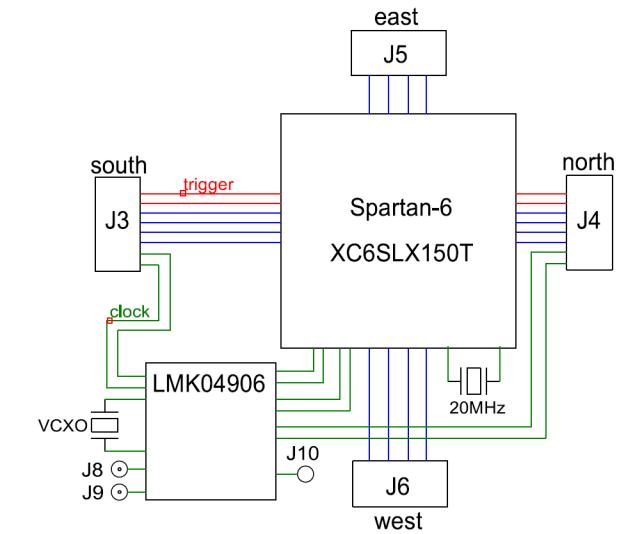

PLL ASIC example: LMK04906 (Texas Instruments) Ultralow Noise Clock Jitter Cleaner and Multiplier With 6 Programmable Outputs

- Input clock: <500MHz

- Output clocks: 284kHz to 2.6GHz

- Internal VCO frequency: 2.6GHz

- Dual Loop PLL architecture

- 25-ps Step Analog Delay Control

- ...

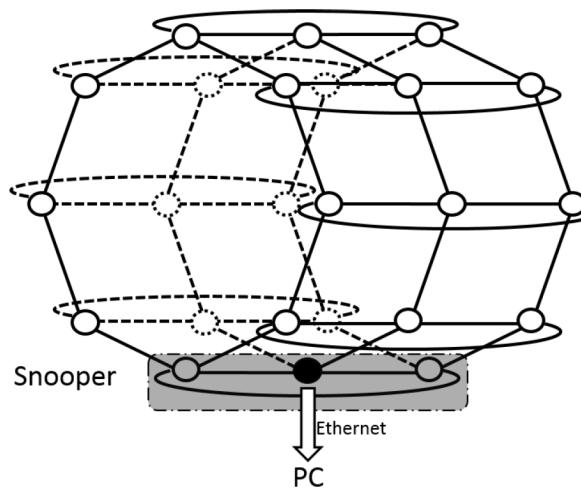

Example of use for clock jitter cleaning and phase offset compensation in a clock distribution network for Positron Emission Tomography (PET)

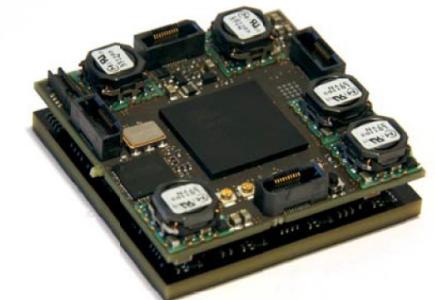

Front side: Tile of the first generation SPADnet sensor

Back side: FPGA board and Power distribution

C. Bruschini, C. Veerappan, et al., A Sensor Network Architecture for Digital SiPM-Based PET Systems, IEEE TRPMS 2, 2018

# Outline

---

12.1.1 Phase-Locked Loops (PLL)

12.1.2 Lock-in Amplifier

12.1.3 Other Tools for Electrical Metrology

Appendix A: PLL Analogies

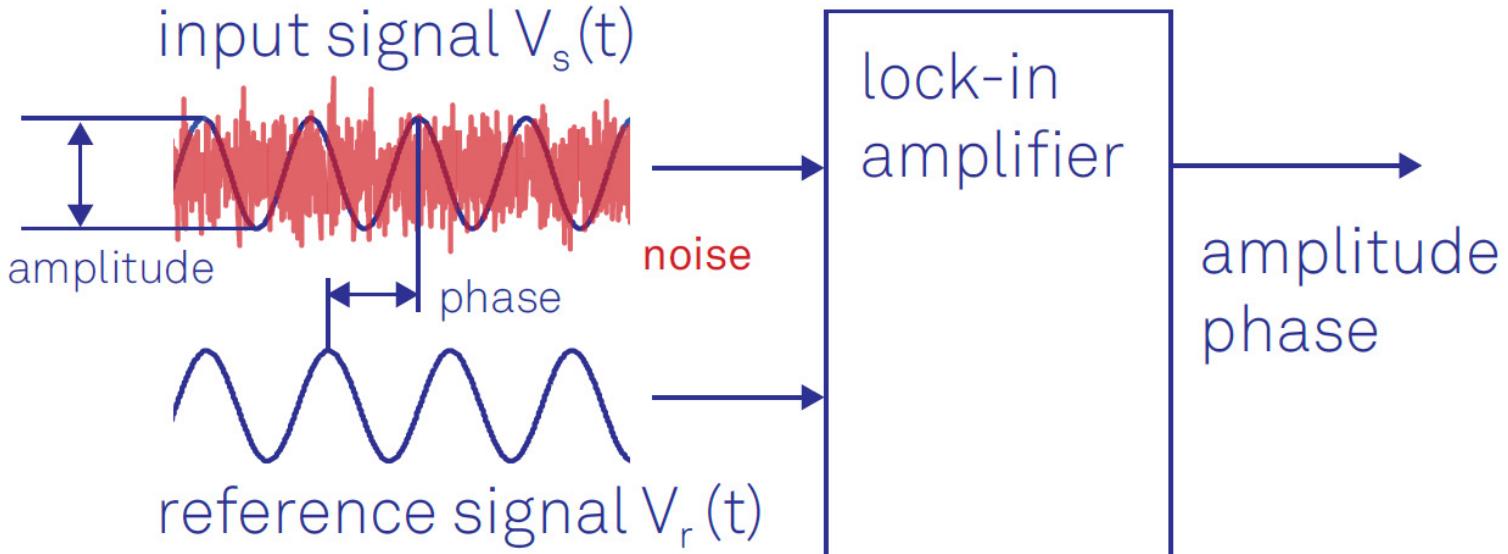

## 12.1.2 PLL Application Example: Lock-in Amplifier

- Amplifier which can extract a signal with a known carrier wave from an extremely noisy environment (signals up to  $10^6$  smaller, in amplitude, than noise = 120 dB!) -> concept of dynamic reserve.

- Trick: use knowledge about a signal's time dependence, or impose it\*.

- Is basically a homodyne detector (i.e. single frequency) followed by a low-pass filter that is often adjustable in cut-off frequency and filter order.

- Traditional (analog): analog frequency mixers and RC filters for the demodulation,

- Digital: digital signal processing, for example, on an FPGA.

$V_r(t)$  (internal reference signal) is usually generated by a PLL locked to the external reference

\*Also: noise is often spread over a much wider range of frequencies than the signal

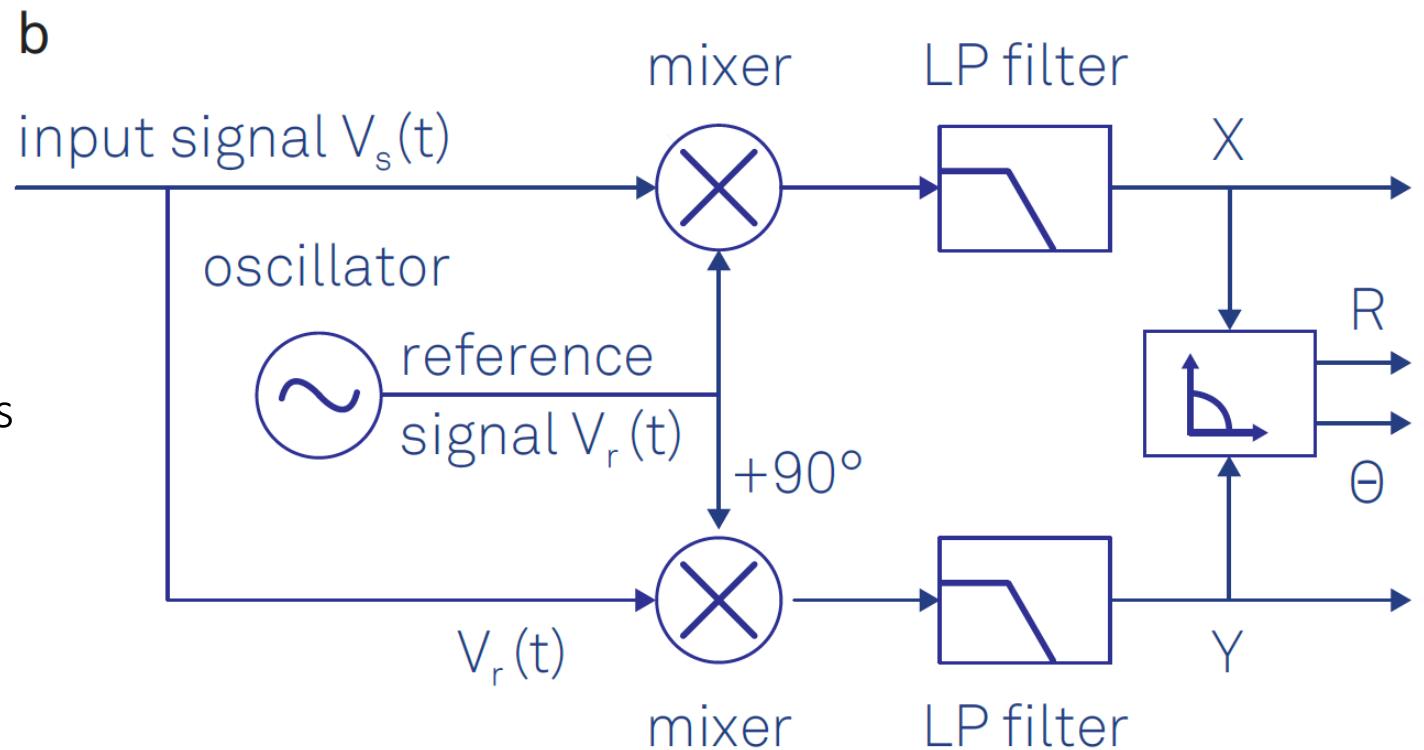

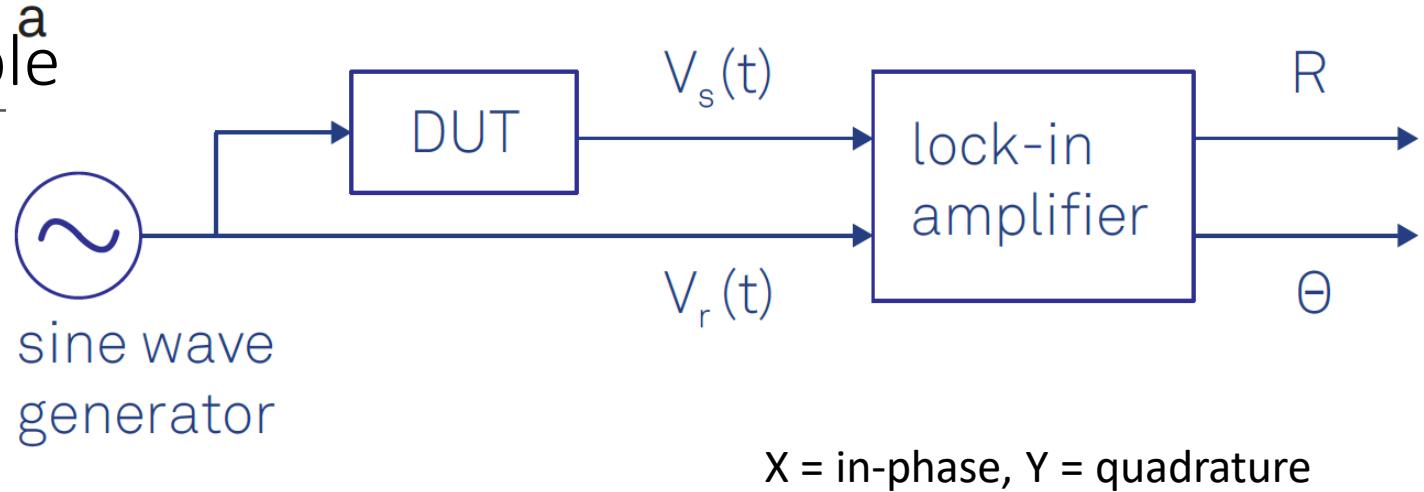

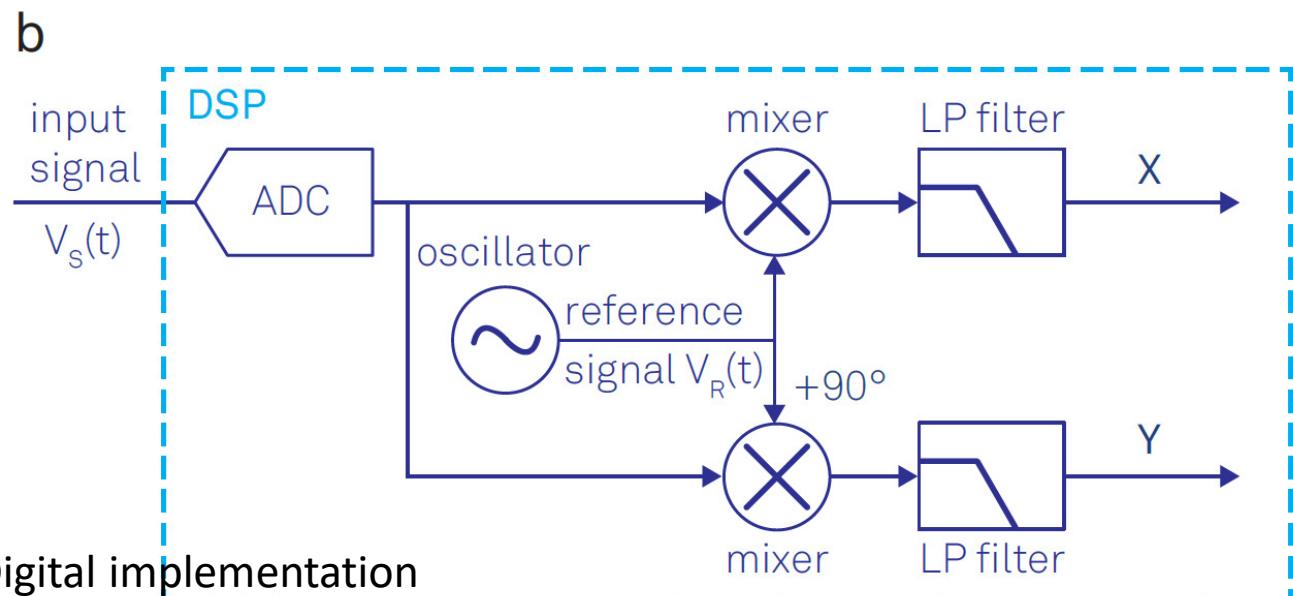

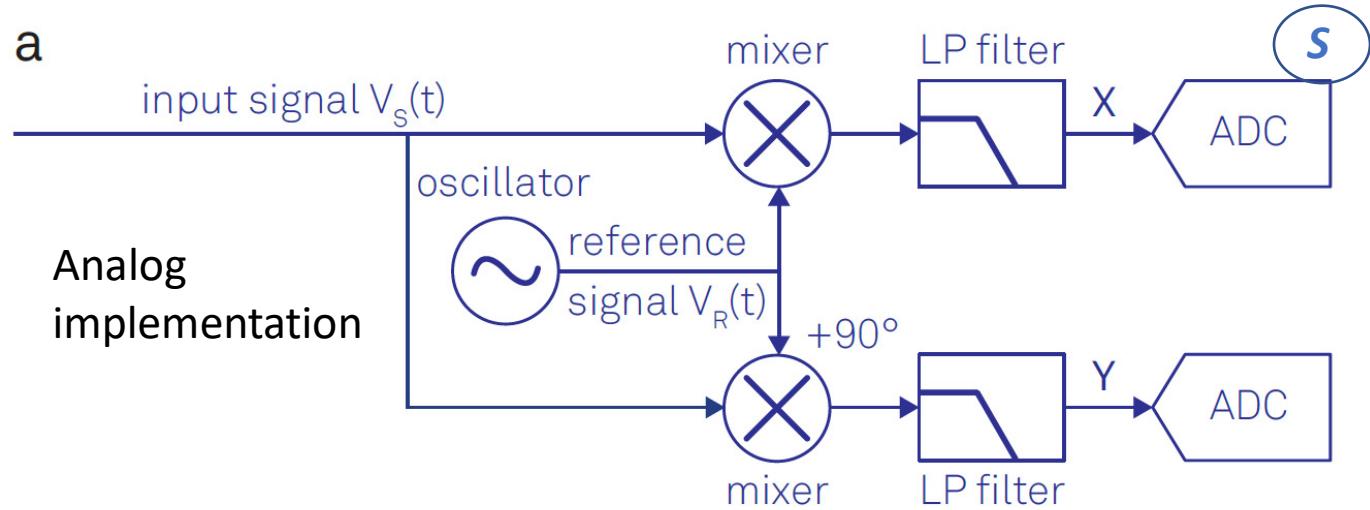

## 12.1.2 Lock-in Amplifier: Principle<sup>a</sup>

A) Typical lock-in set-up: a sinusoidal signal drives the device under test (DUT) and serves as a reference signal. The lock-in outputs the amplitude and phase relative to the reference signal.

B) “Down-mixing”: the input signal is multiplied by the reference signal and a  $90^\circ$  phase-shifted version of the reference signal (sine and cosine demodulation – dual-phase demodulation) ->.

C) “Demodulation”: the mixer outputs are low-pass filtered to reject the noise and the  $2\omega$  component, and finally converted into polar coordinates.

## 12.1.2 Lock-in Amplifier: Principle

---

$$V_s(t) = R \cdot \cos(2\pi f_s t + \phi_s), V_r(t) = \cos(2\pi f_r t)$$

Mixing:  $V_s(t) \cdot V_r(t)$

-> Two components at  $(f_s - f_r)$  and  $(f_s + f_r)$ .

- If  $f_r = f_s$ :  $(f_s - f_r) = 0$  Hz and  $(f_s + f_r) = 2f$ . -> DC component is measurement goal\* (in-phase component, X), the 2f component can be cancelled with an appropriate low-pass filter

- $R, \Theta_r$  calculated by transformation from Cartesian to Polar coords

\*contribution from any signal that is not at the same frequency as the reference signal is attenuated close to zero.

Not discussed here: LP filter characteristics and trade-offs

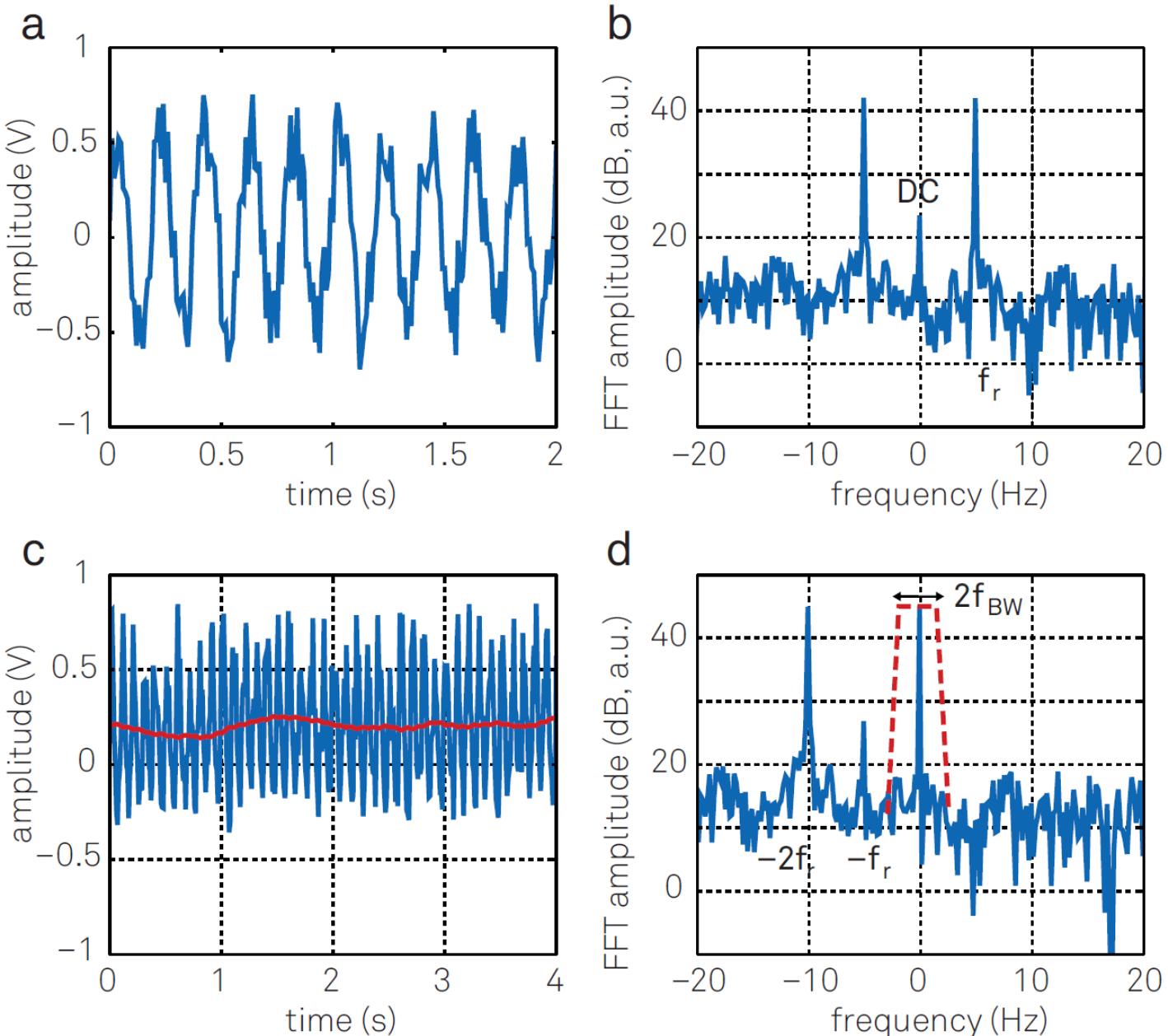

## 12.1.2 Lock-in Amplifier: Example

- (a) TD: Sinusoidal input signal superimposed with noise.

- (b) FD: Same represented in the frequency domain (two symmetric peaks + DC component = offset).

- (c) TD: After mixing with the reference signal (blue trace) and low-pass filtering (red trace).

- (d) FD: the frequency-mixing shifts the frequency components by  $-f_r$ . The filter then picks out a narrow band of  $f_{BW}$  around zero.

## 12.1.2 Lock-in Amplifier: Example

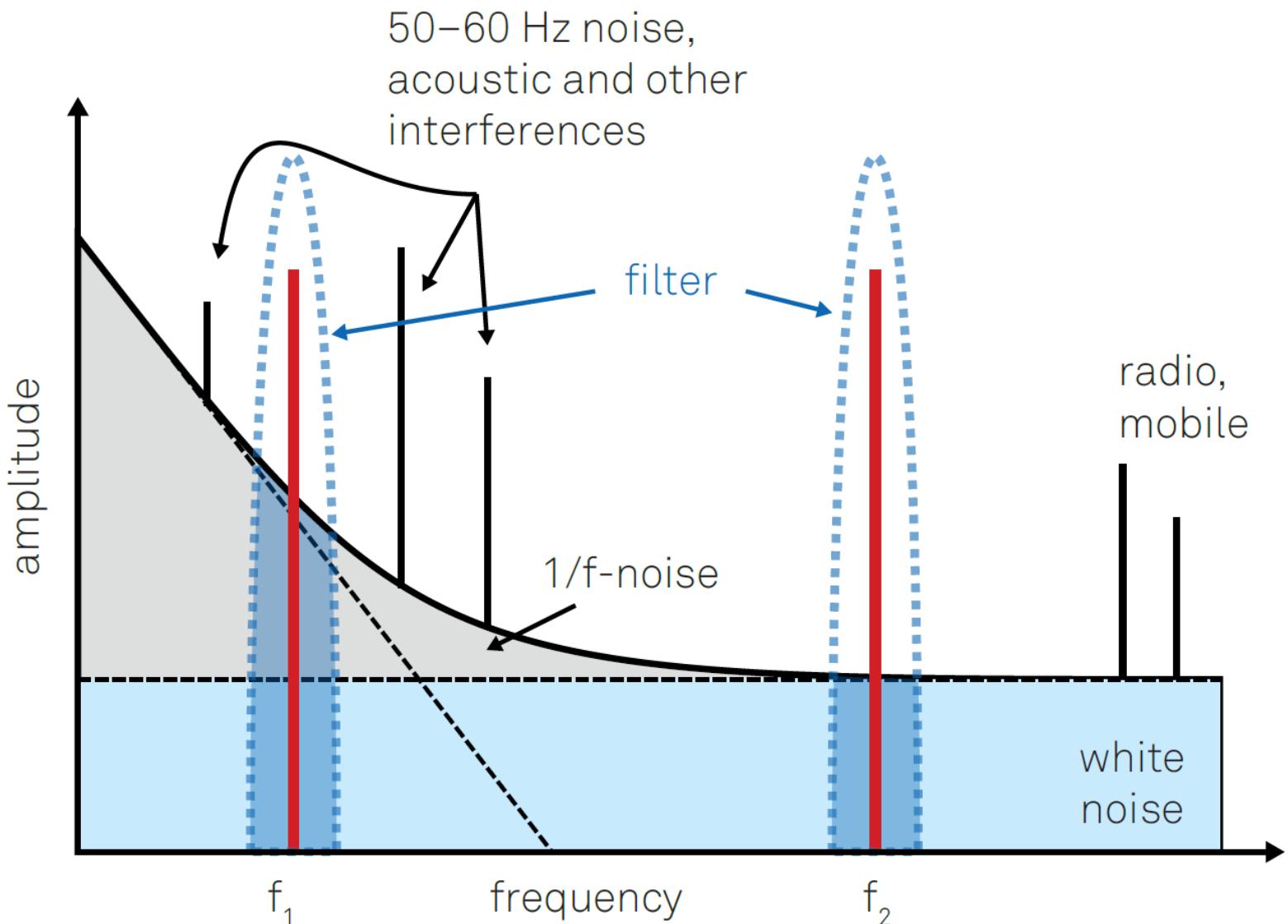

- Qualitative noise spectrum example (typical experiment).

- The measurement frequency should be chosen in a region with small background.

- Here,  $f_2$  will provide better results than  $f_1$  for the same filter bandwidth.

## 12.1.2 Lock-in Amplifier

- Reference signal is usually a sine wave, but not only (e.g. square wave -> captures all odd harmonics).

- NB: when the signal-to-noise ratio is low, a strong, clean reference signal is required, at the same frequency as the received signal. Might not be always available -> instrument limitations.

- Used as precision AC voltage and AC phase meters, noise measurement units, impedance spectrometers, network analyzers, spectrum analyzers and phase detectors in phase-locked loops.

Digital implementation

(immediate conversion to the digital domain – all subsequent steps are carried out numerically)

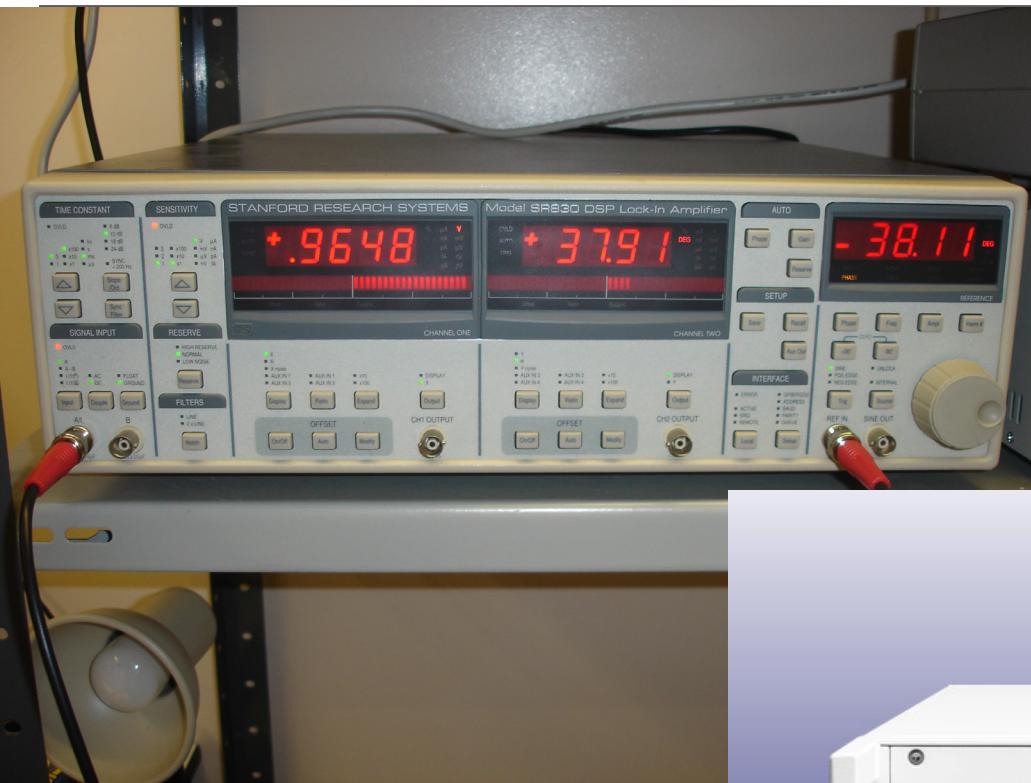

## 12.1.2 Lock-in Amplifier: Examples

Stanford Research Instruments,

Analog Lock-in

By Nuno Nogueira (Nmnogueira) -

Self-made, CC BY-SA 2.5,

<https://en.wikipedia.org/w/index.php?curid=13431432>

Zurich Instruments, Digital Lock-in

EN Wikipedia Lock-in amplifier

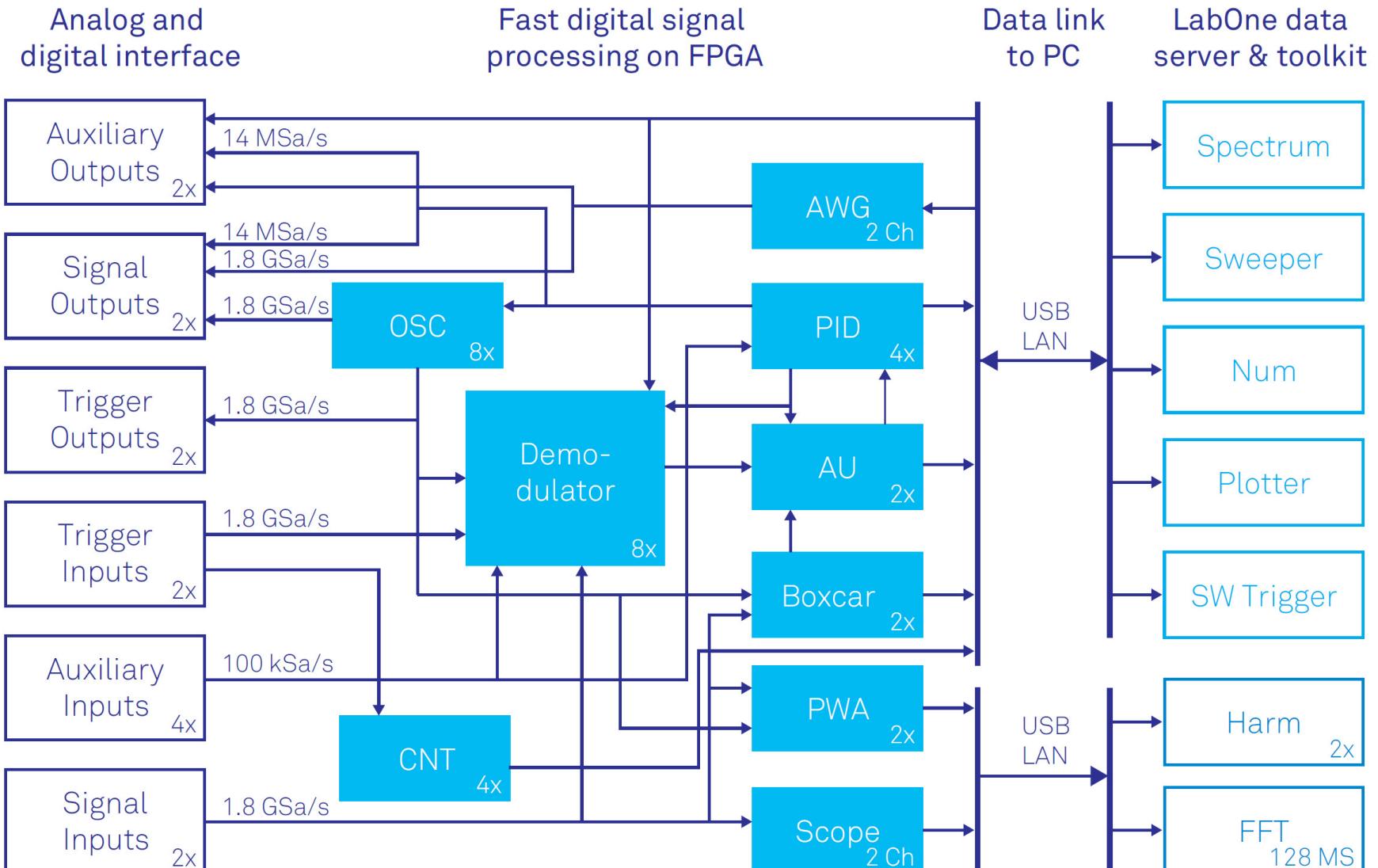

## 12.1.2 Lock-in Amplifier: Example of a digital instrument

Zurich

Instruments,

block

diagramme

Multiple

demodulators

-> analyze a

signal with

different filter

settings or at

multiple

different

frequencies

simultaneously.

# Outline

---

12.1.1 Phase-Locked Loops (PLL)

12.1.2 Lock-in Amplifier

12.1.3 Other Tools for Electrical Metrology

Appendix A: PLL Analogies

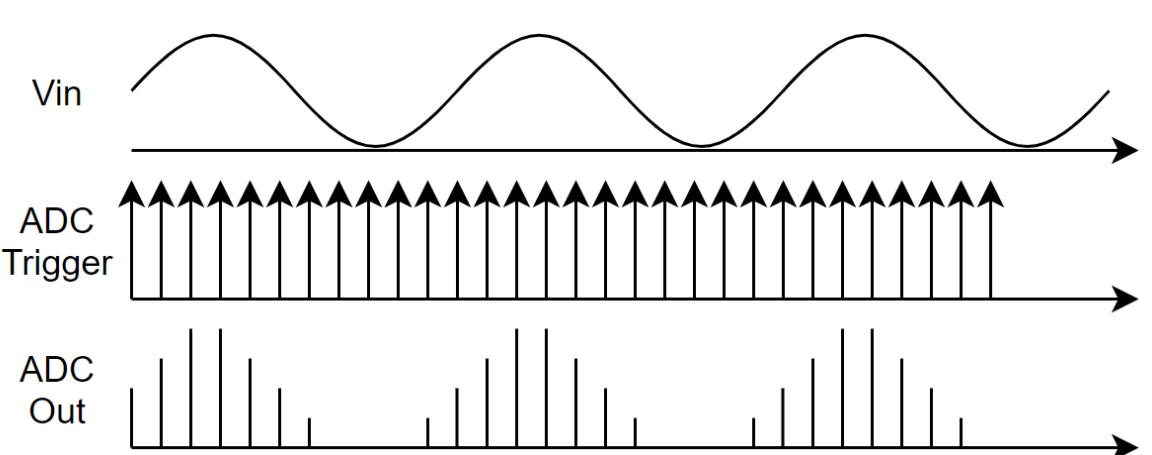

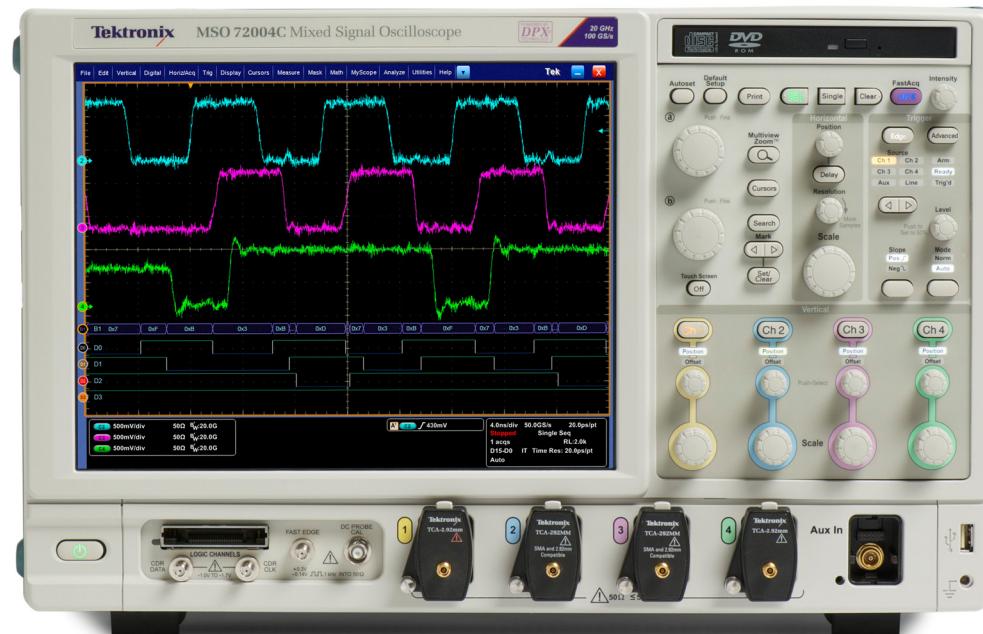

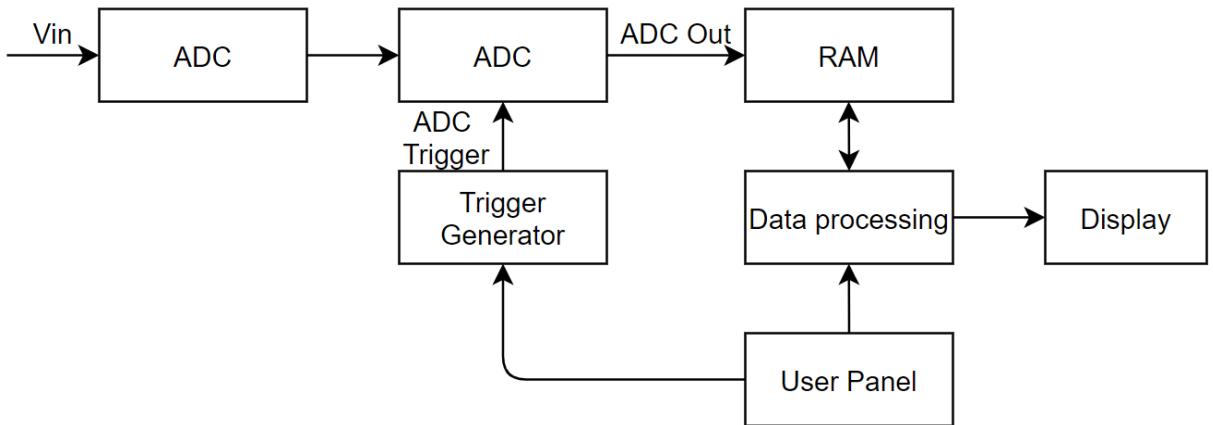

## 12.1.3 (Digital sampling) Oscilloscope

- They sample and display voltages variations in the time domain.

- Provide different trigger modes to capture the desired signal's variation.

- Provides DFFT operation to analyze the frequency domain.

Example: Tektronix MSO72004C - Bandwidth up to 23GHz, 4 Channels, 500Msamples record length, up to 50Gsamples/s

Tektronix, MSO/DPO70000

## 12.1.3 (Digital sampling) Oscilloscope Example

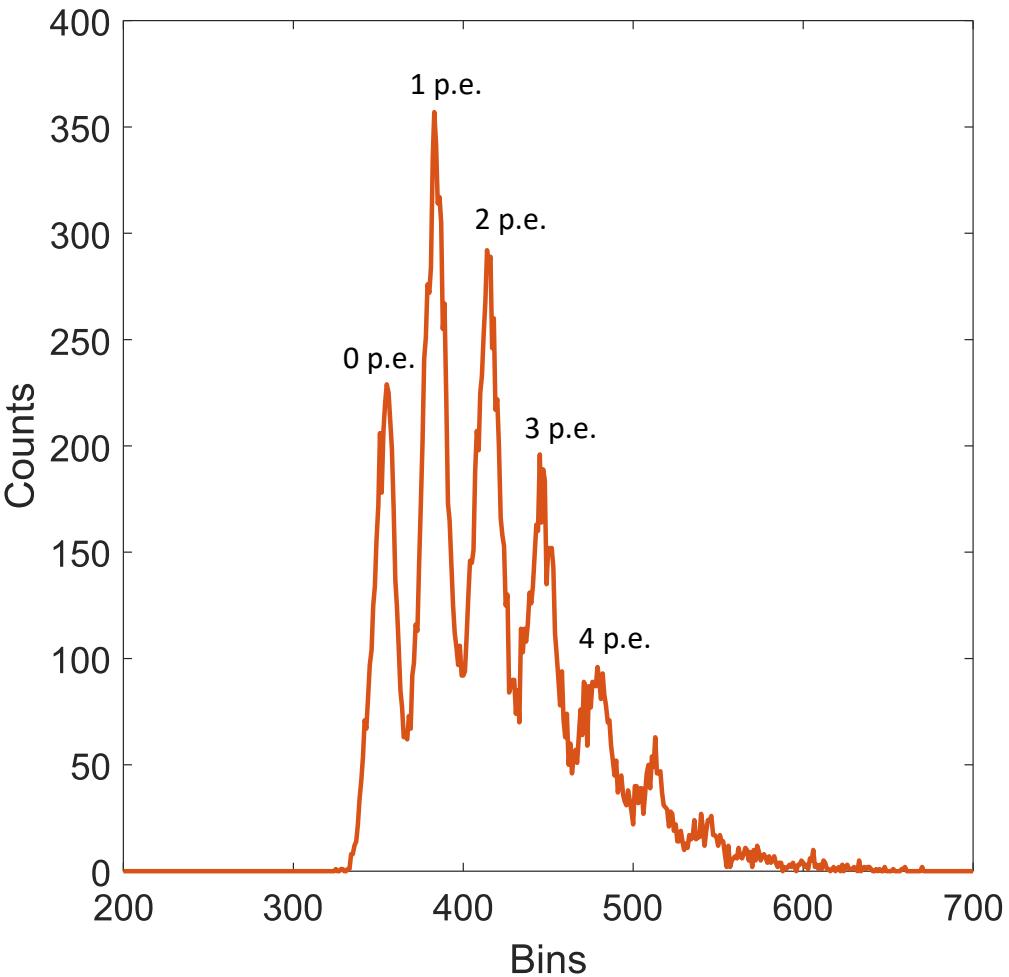

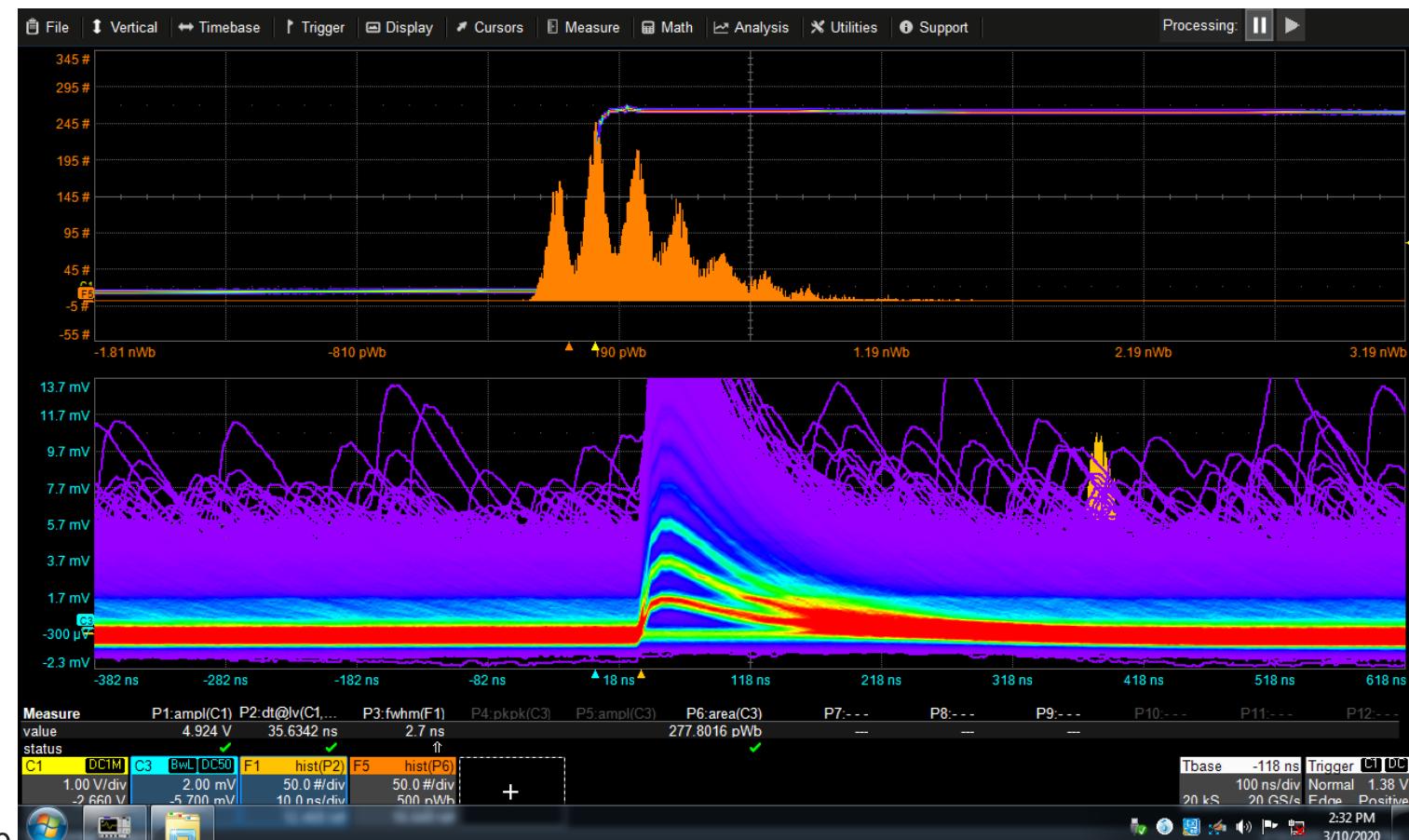

p.e. = photoelectron

Output signal from an analog silicon photomultiplier (SiPM) at very low light levels – “persistence” function allows to visualise very weak but repetitive signals

Courtesy A. Muntean (EPFL-AQUA)

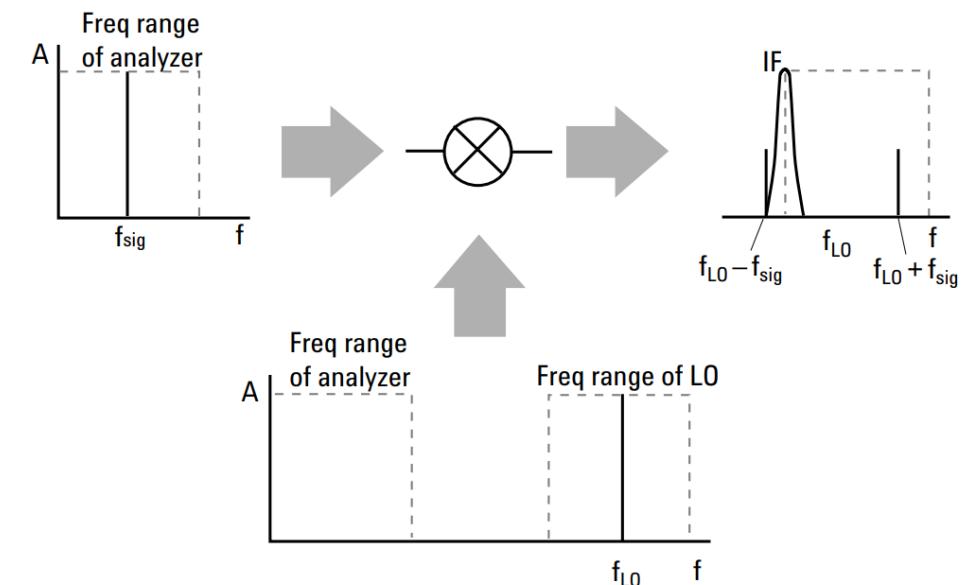

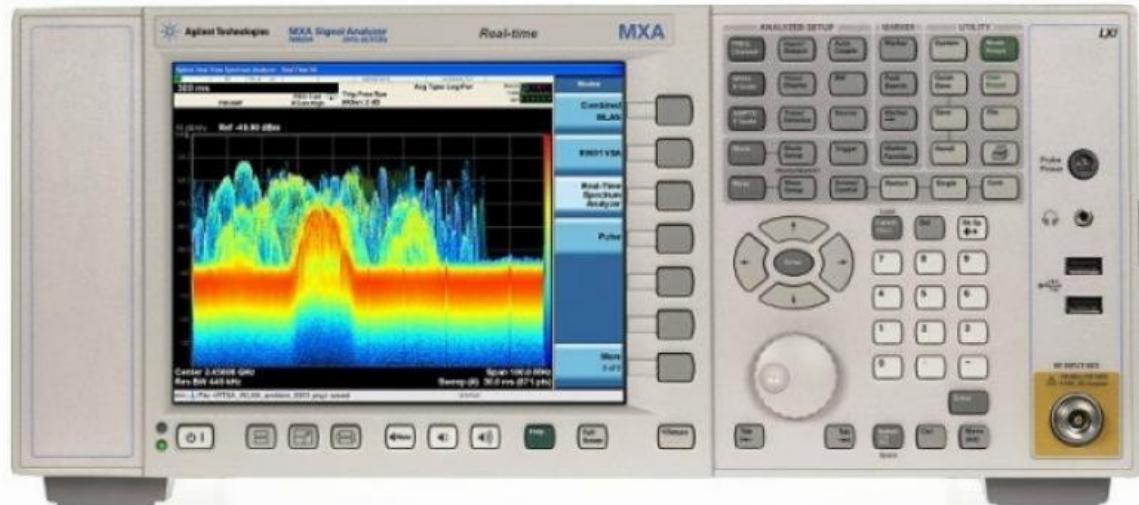

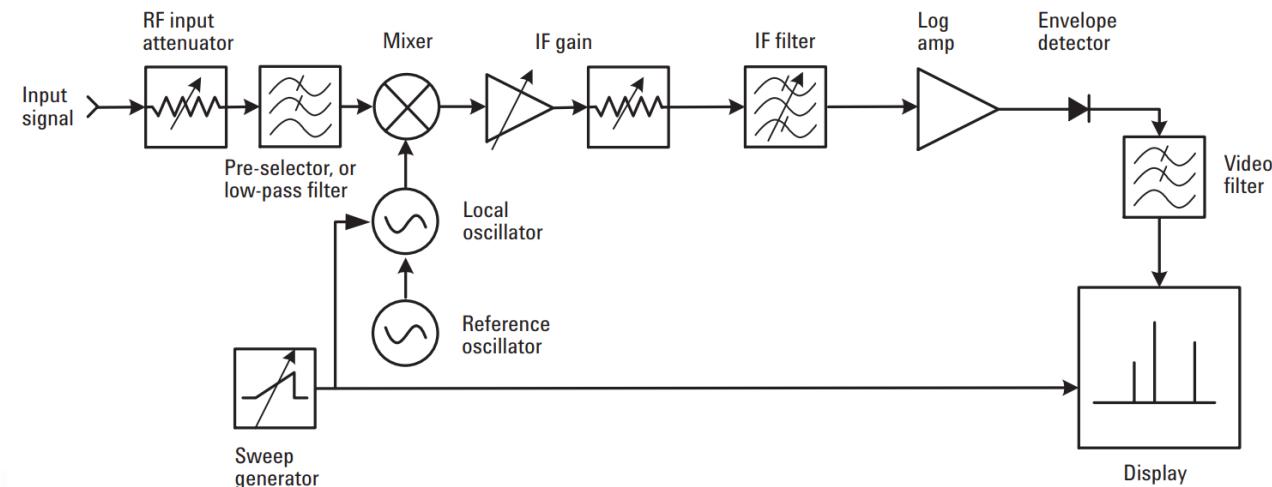

### 12.1.3 Spectrum Analyzers

- Spectrum analyzers show the frequency domain of a repetitive input signal.

- It uses a frequency sweeper to generate the spectrum frequencies and mixes these frequencies with the input signal.

- Logarithmic amplifier is used to translate the output scale from linear to decibel.

## 12.1.3 : Oscilloscopes vs. Spectrum Analyzers

---

Rule of thumb used to be:

- Frequency-domain measurements (output frequency, band power, signal bandwidth, etc.) -> spectrum analyzer

- Time domain measurements (pulse width and repetition rate, signal timing, etc.) -> oscilloscope

- Nowadays, the lines between these two platforms are blurred –for example, oscilloscopes start incorporating FFT techniques -> frequency-domain data!

<https://www.rs-online.com/designspark/do-i-need-a-spectrum-analyzer-or-an-oscilloscope>

# Outline

---

- 12.1.1 Phase-Locked Loops (PLL)

- 12.1.2 Lock-in Amplifier

- 12.1.3 Other Tools for Electrical Metrology

## Appendix A: PLL Analogies

# Acknowledgments

---

- Bedirhan Ilik (TA 2019)

# Appendix A: PLL – Automobile Race Analogy

---

- As an analogy of a PLL, consider an auto race with two cars. One represents the input frequency, the other the PLL's output VCO frequency.

- Each lap corresponds to a complete cycle. The number of laps per hour (a speed) corresponds to the frequency. The separation of the cars (a distance) corresponds to the phase difference between the two oscillating signals.

- During most of the race, each car is on its own and free to pass the other and lap the other. This is analogous to the PLL in an unlocked state.

EN Wikipedia *Phase-locked loop*; [https://en.wikipedia.org/wiki/Phase-locked\\_loop#Practical\\_analogies](https://en.wikipedia.org/wiki/Phase-locked_loop#Practical_analogies)

# Appendix A: PLL – Automobile Race Analogy

---

- However, if there is an accident, a [yellow caution flag](#) is raised. This means neither of the race cars is permitted to overtake and pass the other car.

- The two race cars represent the input and output frequency of the PLL in a locked state.

- Each driver will measure the phase difference (a fraction of the distance around the lap) between himself and the other race car. If the hind driver is too far away, he will increase his speed to close the gap. If he's too close to the other car he will slow down.

- The result is that both race cars will circle the track in lockstep with a fixed phase difference (or constant distance) between them. Since neither car is allowed to lap the other, the cars make the same number of laps in a given time period.

- Therefore the frequency of the two signals is the same.

# Appendix A: PLL – Clock Analogy

---

- Phase can be proportional to time, so a phase difference can be a time difference. Clocks are, with varying degrees of accuracy, phase-locked (time-locked) to a master clock.

- Left on its own, each clock will mark time at slightly different rates. A wall clock, for example, might be fast by a few seconds per hour compared to the reference clock at [NIST](#). Over time, that time difference would become substantial.

- To keep the wall clock in sync with the reference clock, each week the owner compares the time on his wall clock to a more accurate clock (a phase comparison), and he resets his clock.

- Left alone, the wall clock will continue to diverge from the reference clock at the same few seconds per hour rate.

# Appendix A: PLL – Clock Analogy

---

- Some clocks have a timing adjustment (a fast-slow control). When the owner compared his wall clock's time to the reference time, he noticed that his clock was too fast.

- Consequently, he could turn the timing adjust a small amount to make the clock run a little slower (frequency).

- If things work out right, his clock will be more accurate than before.

- Over a series of weekly adjustments, the wall clock's notion of a second would agree with the reference time (locked both in frequency and phase within the wall clock's stability).

- An early [electromechanical](#) version of a phase-locked loop was used in 1921 in the [Shortt-Synchronome clock](#).